网友您好, 请在下方输入框内输入要搜索的题目:

题目内容

(请给出正确答案)

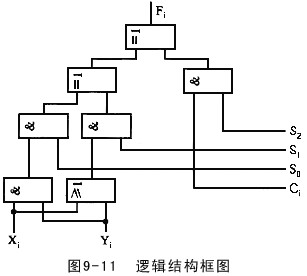

图9-11是一个逻辑结构框图。根据此图判断S2、S1、S0为(17)时,Fi必为0。S2、S1、S0为(18)时,逻辑运算Fi=Xi+Yi成立(图中的符号说明:&为逻辑与,≥1为逻辑或,=1为异或)。

A.0 0 0

B.0 0 1

C.0 1 0

D.0 1 1

参考答案

更多 “ 图9-11是一个逻辑结构框图。根据此图判断S2、S1、S0为(17)时,Fi必为0。S2、S1、S0为(18)时,逻辑运算Fi=Xi+Yi成立(图中的符号说明:为逻辑与,≥1为逻辑或,=1为异或)。A.0 0 0B.0 0 1C.0 1 0D.0 1 1 ” 相关考题

考题

下列地化参数中可以解释为油层的一组是()。

A、S0=0.2358,S1=15.2375,S2=5.2375B、S0=0.0028,S1=1.2372,S2=2.0083C、S0=0.0037,S1=1.0237,S2=1.1517D、S0=0.1347,S1=2.0705,S2=1.5127

考题

图1是一个逻辑结构框图。根据此图判断S2、S1、S0为(56)时,Fi必为0。S2、S1、 S0为(57)时,逻辑运算Fi=Xi+Yi成立(图中的符号说明:为逻辑与,≥1为逻辑或,=1为异或)。A.0 0 0B.0 0 1C.1 0 0D.0 1 1

考题

某正逻辑74LS181,加电稳定后,若要使其完成A减B运算,则应将以下信号设置为()。A.M=0,S3、S2、S1、S0=0110,Cn=0B.M=0,S3、S2、S1、S0=0110,Cn=1C.S3、S2、S1、S0=0110,M、Cn任意D.以上都不对

考题

某正逻辑74LS181,加电稳定后,S3、S2、S1、S0=0001,M=0,Cn=1,若输入为A=1101,B=0011,则输出应为()。A.10000B.0000,且Cn+4=1C.1111D.0000,且Cn+4=0

考题

假设$s0中存放着数组A的起始地址 数组A的定义为:int A[400]; 以下这段MIPS代码的功能是什么? addi $t1, $s0, 1600 addi $s2 $zero, 0 addi LOOP: lw $s1, 0($s0) add $s2, $s2, $s1 lw $s1, 4($s0) add $s2, $s2, $s1 addi $s0, $s0, 8 bne $t1, $s0, LOOPA.int result=0; for (i=400; i>0; i--) { result += A[i]; }B.int result=0; for (i=0; i<400; i+=2 ) { result += A[i]; result += A[i+1]; }C.int result=0; for (i=400; i>0; i-=2) { result += A[i]; result += A[i+1]; }D.int result=0; for (i=0; i<1600; i+=8 ) { result += A[i]; result += A[i+4]; }

考题

假定DFA M=({s0, s1, s2}, {a,b}, f, s0, {s2}),且有如下转换关系: f(s0,a)=s1 f(s0,b)=s2 f(s1,a)=s1 f(s1,b)=s2 f(s2,a)=s2 f(s2,b)=s1 试给出状态转换图与状态转换矩阵。

考题

已知如下对输出逻辑的描述代码,state为当前状态,out为状态机输出。由此可知该状态机为Mealy型状态机。 always @(state) case (state) S0: out = 0; S1: out = 0; S2: out = 1; S3: out = 1; endcase

考题

下列Moore型状态机采用Verilog语言说明部分正确的是:A.parameter [2:0] s0=0, s1=1,s2=2,s3=3,s4=4; reg [2:0] current_state, next_state;B.parameter [1:0] s0=0, s1=1,s2=2,s3=3,s4=4; reg [1:0] current_state, next_state;C.TYPE FSM_ST IS (s0, s1,s2,s3,s4); SIGNAL current_state, next_state: FSM_ST;D.typedef enum {s0, s1,s2,s3,s4} type_user; type_user current_state, next_state

考题

11、已知如下对输出逻辑的描述代码,state为当前状态,out为状态机输出。由此可知该状态机为Mealy型状态机。 always @(state) case (state) S0: out = 0; S1: out = 0; S2: out = 1; S3: out = 1; endcase

热门标签

最新试卷