网友您好, 请在下方输入框内输入要搜索的题目:

题目内容

(请给出正确答案)

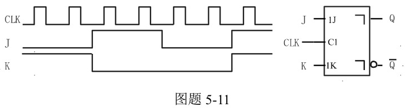

画出图题5-11所示的脉冲JK触发器输出Q端的波形,输入端J K与CLK的波形如图所示。(设Q初始状态为0)

参考答案

更多 “ 画出图题5-11所示的脉冲JK触发器输出Q端的波形,输入端J K与CLK的波形如图所示。(设Q初始状态为0) ” 相关考题

考题

图4-27(a),(b)分别示出了触发器和逻辑门构成的脉冲分频器电路,CP脉冲如图4-27(c)所示,各触发器的初始状态皆为0.(1)试画出图4-27(a)的Q1、Q2和F的波形.(2)试画出图4-27(b)的Q1、Q2和Y的波形.

考题

由两个主从型JK触发器组成的电路如图(a)所示,设Q1、Q2的初始态是00,已知输入信号A和脉冲信号CP的波形,如图(b)所示,当第一个CP脉冲作用后,输出将为( )。

A.00

B.01

C.10

D.11

考题

欲使JK触发器按Qn+1=Qn工作,可使JK触发器的输入端()。A、J=K=0B、J=Q,K=Q’C、J=Q’,K=QD、J=Q,K=0E、J=0,K=Q’

热门标签

最新试卷