网友您好, 请在下方输入框内输入要搜索的题目:

题目内容

(请给出正确答案)

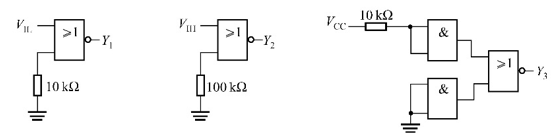

试确定图题 3-25所示74HC门电路的输出状态(设电源Vcc为5 V)。

图题3-25

参考答案

更多 “ 试确定图题 3-25所示74HC门电路的输出状态(设电源Vcc为5 V)。图题3-25 ” 相关考题

考题

写出图题3-27所示电路的逻辑函数式。若是每个门的loL (max)= 20mA, VoL(max)=0.25V,假设Y端连接10个TTL负载。试求电源电压是5V情况下的最小上拉电阻值。图题3-27

考题

在图题10-1所示的电路中,已知R1=10kΩ, R2=30kΩ,其中CMOS非门电路的电源电压Vcc=6V。①计算该电路的正向阈值电压VT+、负向阈值电压VT-和回差电压△VT。②画出该电路的传输特性曲线。③画出图示波形输入下的输出电压Vo波形。

考题

试计算图题11-4所示电路的输出电压Vo。答案:由图可知,D3~Do=0101因此输出电压为:5.8位输出电压型R/2R电阻网络D/A转换器的参考电压为5V,若数字输入为10011001,该转换器输出电压Vo是多少?

考题

如果将TTL逻辑门电路的输出采用下列接法会产生什么样的结果,试说明原因? (1)输出直接接地; (2)输出端直接接电源VCC=+5V; (3)多个输出端并接一起。

热门标签

最新试卷